# RF Direction of Arrival Estimation Using a Linear Antenna Array

Final Report

O. Johnson, E. Pipe, L. Carslake and W. Sam

06 May 2019

# Abstract

Modern communication and sensing systems are becoming increasingly dependant on knowing the position of a electromagnetic source. This information can be used to optimise data throughput of a mobile communications system, or successfully track and locate objects in an increasingly busy electromagnetic environment. Phased Array Antennas are becoming increasingly utilised in small, low cost systems incorporating higher levels of DSP in commercially available products.

This report details the design, construction and testing of a full phased array system which demonstrates the application of several different Direction of Arrival (DOA) calculation methods. The completed system includes a fully operational Radio Frequency (RF) data acquisition system and provides a platform for further research into array signal processing. Several different algorithms have been demonstrated to operate successfully with this system in a reflective environment.

# Contents

| 1 | Intro  | luction .  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|---|--------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 2 | Litera | ture revie | ew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|   | 2.1    | Phased     | Antenna Arrays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|   | 2.2    | Direct (   | Conversion IQ Radio Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|   | 2.3    | Directio   | on of Arrival (DOA) algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|   | 2.4    |            | Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 3 | Aims   | and Obje   | ectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 4 | Meth   | odology    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|   | 4.1    | System     | Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|   | 4.2    | RF From    | nt End                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|   |        | 4.2.1      | Antennas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|   |        | 4.2.2      | Low Noise Amplifiers (LNAs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|   |        | 4.2.3      | AD8348 Demodulator Stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|   |        | 4.2.4      | Local Oscillator (LO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|   |        | 4.2.5      | Anti-Aliasing Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|   |        | 4.2.6      | Analog to Digital Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

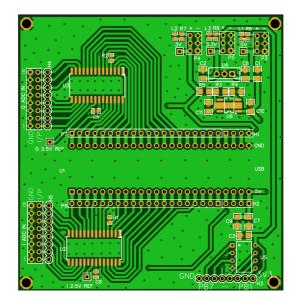

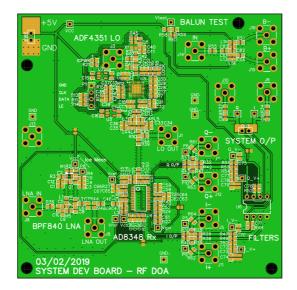

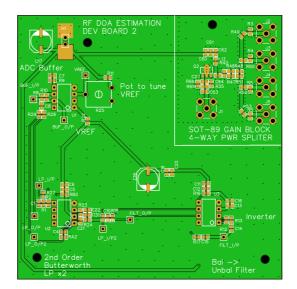

|   |        | 4.2.7      | Development Boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

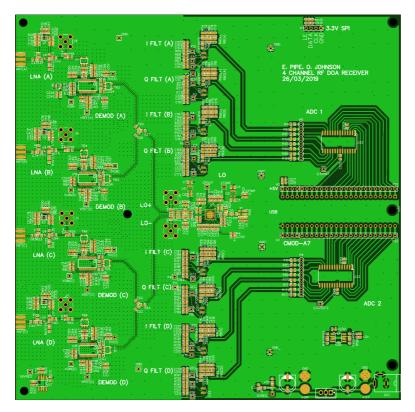

|   |        | 4.2.8      | Final PCB Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|   | 4.3    | FPGA 1     | Digital System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|   |        | 4.3.1      | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|   |        | 4.3.2      | Microblaze                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|   | 4.4    | ADC In     | nterface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|   |        | 4.4.1      | FIFO Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|   |        | 4.4.2      | SRAM Storage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|   | 4.5    | User In    | terface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|   | 4.6    |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|   |        | 4.6.1      | stimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|   |        | 4.6.2      | MATLAB DOA Estimation Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

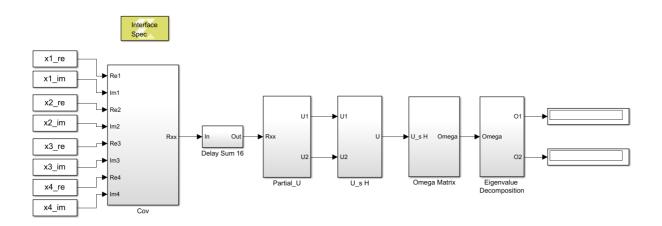

|   |        | 4.6.3      | Simulink DOA Estimation Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|   |        | 4.6.4      | System Integration   43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|   |        | 1.0.1      | System moogration is a second se |  |  |  |  |  |

|   |       | 4.6.5                                                            | Calibration of the receiver                                                  | 43 |  |  |  |

|---|-------|------------------------------------------------------------------|------------------------------------------------------------------------------|----|--|--|--|

| 5 | Resu  | lts and D                                                        | iscussion                                                                    | 45 |  |  |  |

|   | 5.1   | Design and Construct Quadrature RF receiver                      |                                                                              |    |  |  |  |

|   | 5.2   | Design, Simulate and construct phased array antenna              |                                                                              |    |  |  |  |

|   | 5.3   | Design                                                           | and simulate DOA algorithm                                                   | 48 |  |  |  |

|   |       | 5.3.1                                                            | Synthesise quadrature test signals                                           | 48 |  |  |  |

|   |       | 5.3.2                                                            | Simulate DOA algorithm with artificial phase difference and noise (MATLAB) . | 51 |  |  |  |

|   |       | 5.3.3                                                            | Build and Implement Simulink model of DOA algorithm                          | 53 |  |  |  |

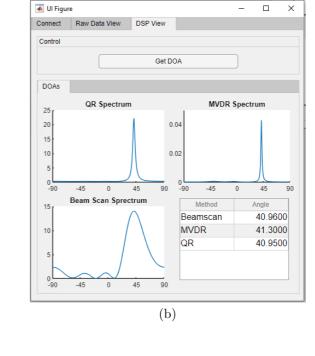

|   | 5.4   | Create                                                           | GUI for presenting data to user                                              | 54 |  |  |  |

|   |       | 5.4.1                                                            | Read data from digital hardware to PC                                        | 54 |  |  |  |

|   |       | 5.4.2                                                            | Integration of DOA algorithm with GUI                                        | 54 |  |  |  |

|   |       | 5.4.3                                                            | Produce DOA result when requested by user                                    | 54 |  |  |  |

|   | 5.5   | Overall                                                          | System Results for DOA Estimation                                            | 55 |  |  |  |

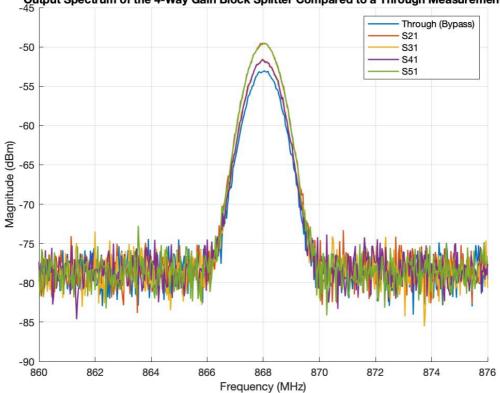

|   |       | 5.5.1                                                            | Hardware Cascade Analysis                                                    | 55 |  |  |  |

| 6 | Conc  | lusion .                                                         |                                                                              | 55 |  |  |  |

| 7 | Reco  | mmendat                                                          | ions and Future Work                                                         | 55 |  |  |  |

|   | 7.1   | Fine tu                                                          | me circuitry                                                                 | 55 |  |  |  |

|   | 7.2   | Printed                                                          | l Antenna                                                                    | 56 |  |  |  |

|   | 7.3   | Autom                                                            | atic Gain Controll (AGC)                                                     | 56 |  |  |  |

|   | 7.4   | Increas                                                          | e the number of elements in the array                                        | 56 |  |  |  |

|   | 7.5   | Extra front end downconversion for higher RF operation - 4G/WiFi |                                                                              |    |  |  |  |

|   | 7.6   | Automatic Calibration for range of input signals                 |                                                                              |    |  |  |  |

|   | 7.7   | Use a f                                                          | aster method of off loading data from the FPGA                               | 56 |  |  |  |

|   | 7.8   | Add ad                                                           | lvanced triggering mechanisms to the FPGA                                    | 57 |  |  |  |

|   | 7.9   | Implem                                                           | nent Algorithm directly on FPGA                                              | 57 |  |  |  |

| 8 | Achie | evement H                                                        | Evaluation                                                                   | 57 |  |  |  |

| 9 | Appe  | endices .                                                        |                                                                              | 61 |  |  |  |

# 1 Introduction

By measuring the difference in phase of an incoming signal from multiple receivers a distance apart, it is possible to calculate the Angle of Arrival (AOA) from which the signal came. There are various algorithms that can calculate the AOA, each applicable for different types of environments, but a constant through every method is the need to capture the signal. In order to capture AOA information about an electromagnetic signal, an antenna array is needed. This consists of multiple antennas in a known and specific geometry.

Knowing the direction from which a signal source is coming from is useful for tracking and locating objects. This sort of signal processing has been used extensively in Radar, however more recently with the advent of 5G, location and tracking of a transceiver is being used to optimise the transmission and reception of signals for mobile users.

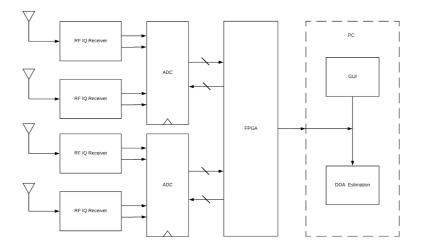

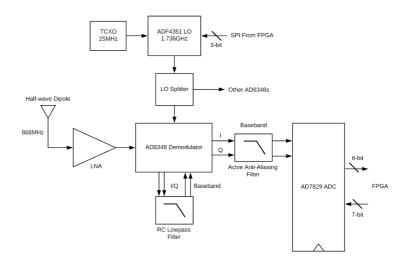

In this project the design and construction of a 4-element antenna array and RF receiver, including digitization and signal processing, to calculate the AOA of an incoming wave is demonstrated. A custom RF front end passes incident signals to an ADC, where it is then sampled and passed through an FPGA into a Matlab Graphical User Interface (GUI) where a number of different algorithms including beamscan, Minimum Variance Distortionless Response (MVDR) and QR decomposition methods are used to successfully estimate the Direction of Arrival (DOA).

For this specific system, a receive chain composed of custom antennas, a transistorised LNA, a 50MHz-1GHz IQ demodulator IC, active filtering for anti-aliasing, diode clipper circuits for ADC protection, and digitisation in ADCs. Once digitised, an FPGA offers flexibility and performance to implement DOA algorithms, storage of samples and transmission to the GUI. From the GUI the user is able to control the system and view the received signals.

# 2 Literature review

# 2.1 Phased Antenna Arrays

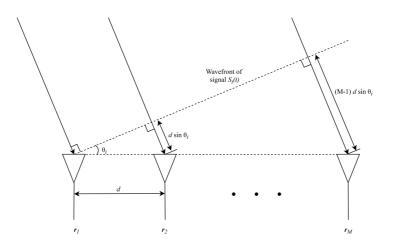

For a source which is a distance away from the antenna array which is significantly larger than the element separation distance, the source is defined as being in the Far-Field [1]. This implies that the antennas do not perceive near-field coupling (only radiated fields) and the spherical wavefronts of the propagating waves become so large that they can be approximated as straight lines. This leads to the condition illustrated in Figure 1.

Figure 1: Uniform Linear Array (ULA).

The diagram in figure 1 shows the derivation of values for signals received by an *M*-element ULA with spacing of *d* between elements. The incoming signal wavefront is denoted as  $S_i(t)$  and  $r_1$ ,  $r_2$  and  $r_M$  are the signals received at each sensor. A given signal located at  $\theta_i$  from the on-axis position of the antennas results in a phase shift in signal received by each element of the array, as the signal at each subsequent sensor travels a further

$d \sin \theta_i$ . Hence the maximum extra distance travelled is  $(M-1) d \sin \theta_i$ . From this diagram, it is possible to see that a signal placed perpendicular to the array will have no phase shift between the incoming signals at each sensor and that by manipulating the data received, it is possible to determine the direction of arrival (DOA) angle [3].

A simple method for determining the angle of arrival is the manipulation of the phased array geometry. With a known distance between elements, the time delay can be found:

$$s = d \sin \theta$$

$s = \frac{v}{t}$   $t = \frac{d \sin \theta}{f \lambda}$   $d = \frac{\lambda}{2} \rightarrow t = \frac{\sin \theta}{2f}$

If the first signal occurs at time  $t_1 = 0$ , The phase shift of a signal can be written as:

$$\phi = 2\pi \frac{t_2 - t_1}{T} = 2\pi f t$$

The the two equations can be related and rearranged for angle  $\theta$ :

$$\phi = 2\pi f\left(\frac{\sin\theta}{2f}\right) = \pi \sin\theta \quad \to \qquad \theta = \sin^{-1}\left(\frac{\phi}{\pi}\right) \tag{1}$$

#### 2.2 Direct Conversion IQ Radio Receiver

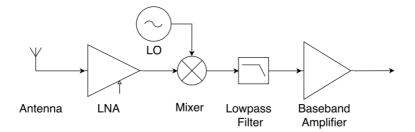

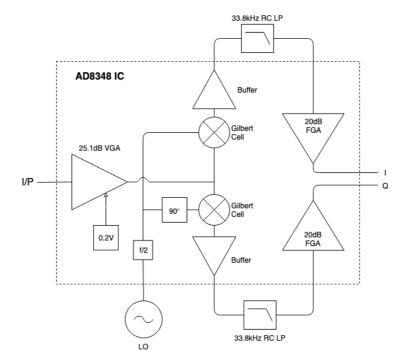

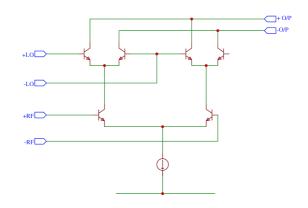

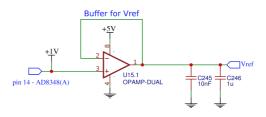

Figure 2: Example direct conversion receiver architecture. RF signal is amplified in a low noise amplifier (LNA), mixed to to baseband, low-pass filtered to prevent aliasing and then amplified and buffered at baseband to drive an ADC..

A direct conversion IQ receiver system is shown in figure 2. The receiver features a single mix down stage, digitising at IF or baseband. This provides a compromise between a standard superheterodyne receiver, and a fully digitised front end. Through the use of a single mix down stage, there is much less complicated analog circuitry than in a superhet, whilst being able to use a cheaper, and less power hungry ADC than in a directly sampling a signal at RF [2].

#### 2.3 Direction of Arrival (DOA) algorithms

The received received signals at the ULA (as shown in figure 1) can be described through the equation [3, 4]:

$$\mathbf{r}(t) = \mathbf{AS}_i(t) + \mathbf{n}(t) \tag{2}$$

Although, DOA angle estimation is reliant on sampling of incoming signals at selected time instants  $t_n$  (n = 1, 2, ..., N), so this can be re-written as:

$$\mathbf{r}(n) = \mathbf{AS}_i(n) + \mathbf{n}(n)$$

Where  $\mathbf{S}_i(n)$  is the incoming signal,  $\mathbf{n}(n)$  is the noise of the signal, M is the number of sensors or elements in the antenna array, and  $\mathbf{A}$  is the array manifold made up of steering vectors which correspond to the L the number of sources:

$$\mathbf{A} = [a(\theta_1), a(\theta_2) \dots a(\theta_L)]$$

(3)

Thus when L = 1:

$\mathbf{A} = \left[ a(\theta_1) \right]$

The steering vector for a single source is:

$$\mathbf{a}(\theta) = [1e^{jk}, 1e^{2jk} \dots 1e^{(M-1)jk}]$$

(4)

where  $k = \frac{2\pi d}{\lambda} \sin \theta$ . If  $d = \frac{\lambda}{2}$  then  $k = \pi \sin \theta$ . It should also be noted that this applies for the evaluation of angles between  $\frac{\pi}{2}$  and  $\frac{-\pi}{2}$ . Since  $\sin \theta = \cos(\frac{\pi}{2} - \theta)$ ,  $k = -\pi \cos \theta$  for the evaluation of angles between 0 and  $\pi$ .

For a single source, the array response matrix is simply the transpose of the steering vectors:

$$\mathbf{a}(\theta) = [1e^{jk}, 1e^{2jk} \dots 1e^{(M-1)jk}]^T$$

which can be calculated through  $\pi$  radians to characterise response of the array.

DOA algorithms often use higher order statistics to the within the processing of the signal data. This assumes that received signal and received noise are independent and have a mean of zero. This results in the spatial array correlation matrix given by:

$$\mathbf{R} = E\{\mathbf{r}(n)\mathbf{r}(n)^H\} = \mathbf{ASA}^H + \mathbf{R}_n \tag{5}$$

If  $\mathbf{R}_n$  is considered to be spatially white, then  $\mathbf{R}_n = \sigma^2 \mathbf{I}$ , with  $\sigma^2$  representing the noise level, and  $\mathbf{I}$  is the identity matrix with dimensions  $M \times M$ . Here  $\mathbf{S}$  is the received incoming signal and H is the complex conjugate transpose or Hermitian transposition.

For a S number of snapshot instances, the correlation matrix of  $\mathbf{R}$  can be simply estimated:

$$\hat{\mathbf{R}} = \frac{1}{S} \sum_{s=1}^{S} \mathbf{r}(n) \mathbf{r}(n)^{H}$$

The minimum number of snapshots corresponds to the number of elements M and the higher the number of snapshots used, the more accurate the estimation.

The most fundamental method of DOA angle estimation is a conventional (delay and sum) beamformer [4], which uses calculated weights to create a beam that can be steered through spatial spectrum and impart various values corresponding to the DOA angle [5].

The limitation of this method is the array aperture since the resolution of the beamformer is inversely proportional.

The beamformer power spectrum that shows the spectral density of the received signals in the spatial domain is given by:

$$P_{BS}(\theta) = \frac{1}{N} \sum_{n=1}^{N} |\mathbf{a}(\theta)^{H} \mathbf{r}(t)|^{2} = \mathbf{a}(\theta)^{H} \,\hat{\mathbf{R}} \,\mathbf{a}(\theta)$$

(6)

Minimum Variance Distortionless Response (MVDR) estimation assumes that signal and noise data is uncorrelated, hence the variance of the system can be simplified to the sum of signal and noise variances and minimised to suppress noise [6]. This method improves on the resolution of the conventional beam former because of the sharper peak outputs [7, 8]. The MVDR spectrum is given by:

$$P_{MVDR}(\theta) = \frac{1}{\mathbf{a}(\theta)^H \,\hat{\mathbf{R}}^{-1} \,\mathbf{a}(\theta)} \tag{7}$$

Another method method is linear decomposition (QR decomposition) estimation which makes use of linear decomposition to produce the signal and noise sub spaces. Unlike MUSIC or ESPRIT algorithms, this method does not use computational complex eigenvalue decomposition (EVD) which makes calculation more feasable on limited processing hardware [9].

For covariance matrix estimate  $\hat{\mathbf{R}}$ :

$$\hat{\mathbf{R}} = Q R = [Q_s \ Q_n] \begin{bmatrix} R_L \\ O \end{bmatrix}$$

(8)

Where  $Q_s$  is the column vector of the signal space, and  $Q_n$  is the column vector of the noise space. The upper triangular matrix  $R_L$  represents the signal space which corresponds to the size (L x M). O is a null matrix of size (M - L) x M. The orthogonality of the Q matrix (in that  $QQ^H = Q^H Q = I$ , and) results in:

$$Q^{H}\,\hat{\mathbf{R}} = Q^{H}\,Q\,R = \begin{bmatrix} Q_{s} \\ Q_{n} \end{bmatrix} [Q_{s}\,Q_{n}] \begin{bmatrix} R_{L} \\ O \end{bmatrix} \rightarrow \begin{bmatrix} Q_{s}^{H}\,\hat{\mathbf{R}} \\ Q_{n}^{H}\,\hat{\mathbf{R}} \end{bmatrix} = \begin{bmatrix} R_{L} \\ O \end{bmatrix}$$

(9)

Substituting in equation (4) for  $\hat{\mathbf{R}}$ , and for uncorrelated sources, A is full rank and S is non-singular:

$$Q_n^H \,\hat{\mathbf{R}} = Q_n^H \, A \, S \, A^H = O \qquad \qquad Q_n^H \, A = O$$

The steering vectors  $a(\theta)$  that are orthogonal to the noise space  $Q_n$  are used to reveal the direction of arrival. Therefore, the angle can be found using a peak search:

$$P_{QR}(\theta) = \frac{1}{||Q_n^H A(\theta)||} = \frac{1}{A^H(\theta) Q_n^H Q_n A(\theta)}$$

(10)

A similar method to the QR peak search method is the Multiple Signal Classification (MUSIC) technique. This requires eigenvalue decomposition of the covariance matrix, which can be calculated using the eigenvalues and eigenvectors [10] according to :

$$A^{H}v_{i} = 0$$

$i = (L+1), (L+2) \dots M$

These eigenvectors can then be concatenated to make up the the noise space  $E_n$ :

$$E_n = [V_{L+1}, V_{L+2} \dots V_M]$$

(11)

Then, perform a peak search for the angle  $\theta$ :

$$P_{MUSIC}(\theta) = \frac{1}{||E_n^H A(\theta)||^2} = \frac{1}{A^H(\theta) E_n E_n^H A(\theta)}$$

(12)

The rotation invariance of a decomposed matrix can also be explored using the Estimation of Signal Parameters via Rotational Invariance Techniques (ESPRIT). This method uses the two subspaces of noise and space to solve eigenvalues to form a matrix that relates the two [3, 4]. A simple method of doing this is by splitting up the array into two which are shifted by one. The selection can be written as:

| $Y_1 = [i_1, i_2 \dots i_{M-1}, 0]$                                                   | $Y_2 = [0, i_2, i_3 \dots i_M]$                                                       |

|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| $Y_1 = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix}$ | $Y_2 = \begin{bmatrix} 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$ |

Where the vector will correspond to the size of the array, with the first or last element being null.  $A_i$  will then be equal to 1. This selects the response matrices:

$$A_1(\theta) = Y_1 A(\theta) \qquad \qquad A_2(\theta) = Y_2 A(\theta)$$

The shift invariant property of the sub arrays can be written as:

$$A_2(\theta) = A_1(\theta) \Phi \tag{13}$$

The array responses and signal eigenvectors span the same subspace, related by a non-singular linear transform T, resulting in:

$$U_S = A(\theta) T \tag{14}$$

Combining with the selection matrices and using the two sub matrices together:

$$U_{S1} = A_1(\theta)T \qquad \qquad U_{S2} = A_2(\theta)T$$

$$T\Psi T^{-1} = \Phi \tag{15}$$

With  $\Psi$  being similar to the matrix  $\Phi$ , the eigen values will be the same. Finding the least squares solution to equation (15) and calculating the eigenvalues ( $e_i = e_1, e_2 \dots$ ) of this solution results in the DOA estimate:

$$\theta_i = \sin^{-1} \left( \frac{angle(e_i)}{2\pi d} \right) \tag{16}$$

The benefit of ESPRIT is that it does not require the searching over a range of  $\theta$  which results in a less computationally intensive calculation [7, 11]. However, some of the operations required to estimate the angle of arrival could be more difficult to implement depending on which platform is being used.

# 2.4 Digital Hardware

The digital hardware within the receiver focuses on the acquisition and processing of the demodulated signal. Acquisition is achieved through the use of an analogue to digital converter (ADC) connected to specialised processors such as a CPU or FPGA. Within these processors, transformations and operations of the digitised signal are performed which implement the signals processing tasks required.

Various types of ADCs are available with the key parameters being speed, sampling rate and resolution. For communication system applications current ADC technology provides a base for sampling at resolutions between 8-12 bits, at sampling rates of Ks/s to 100's Ms/s for an acceptable price. The most common technology for the high-speed ADCs is successive approximation (SAR), moving towards pipelined and flash technologies for higher speed applications.

Current research has focused on improving these 3 parameters, with an example of the current state of the art being a 56Gs/s Time-interleaved ADC with an ENOB of 5.7 bits by K. Sun et al [12]. This design demonstrates the tradeoff between sampling rate and resolution encountered when designing ADCs. An application of highspeed ADCs is the direct sampling of the RF signal without down conversion, affording the advantages of DSP to more of the signal chain, however, designs using this technique are currently restricted due to the limited development and high price of high-speed ADCs.

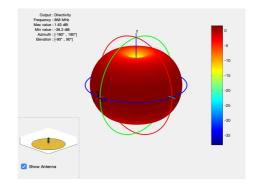

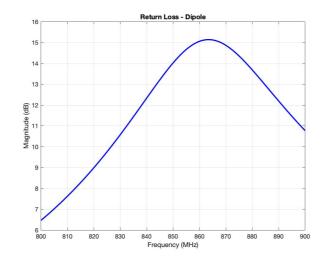

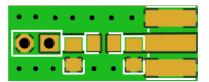

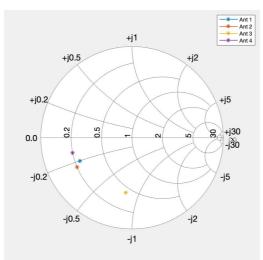

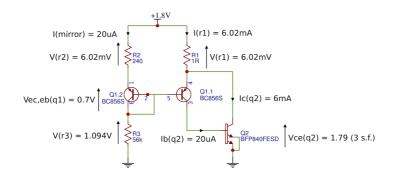

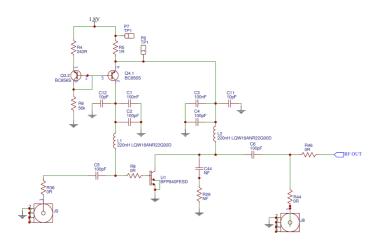

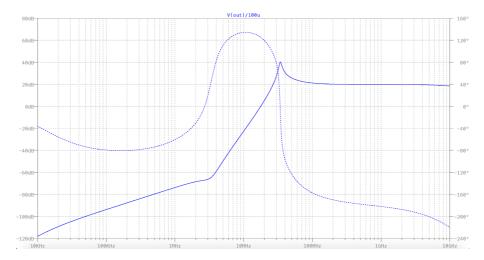

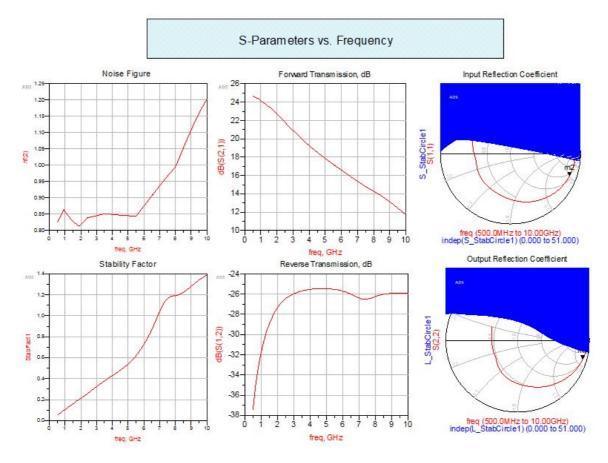

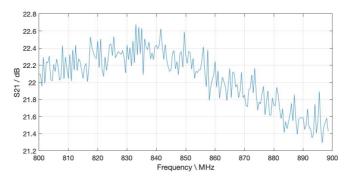

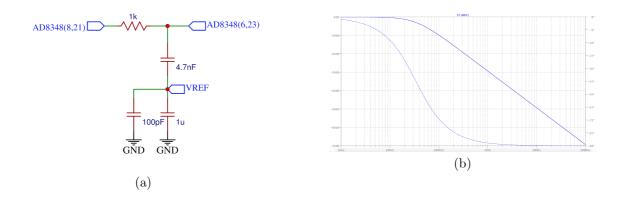

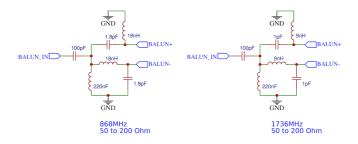

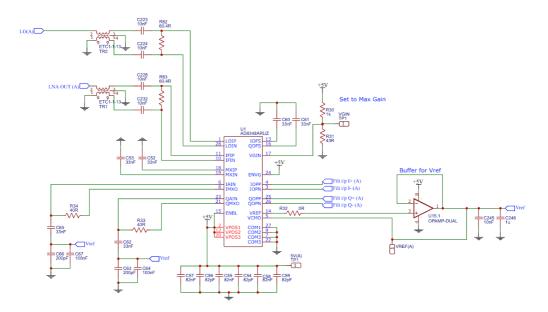

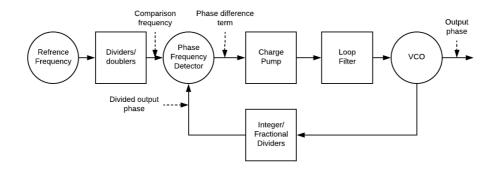

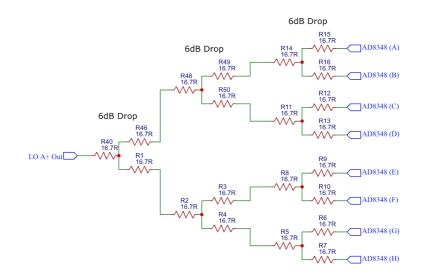

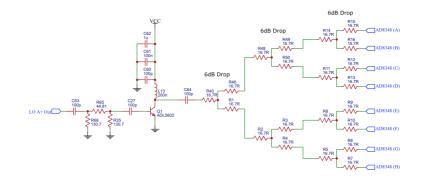

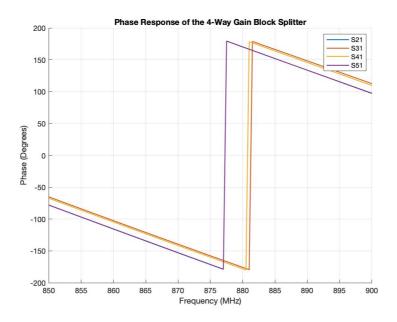

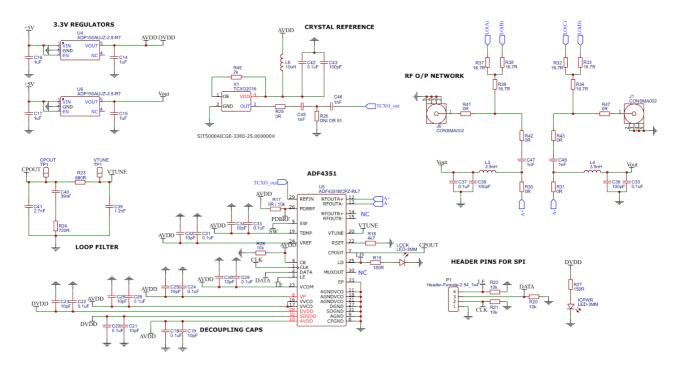

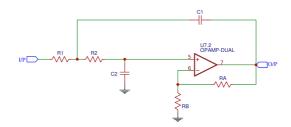

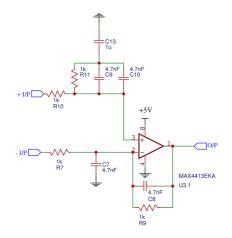

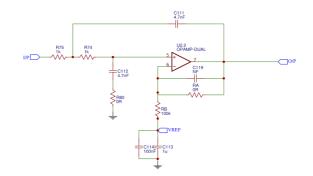

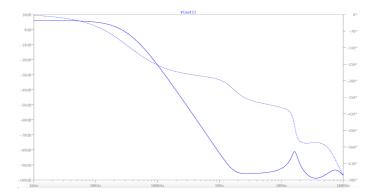

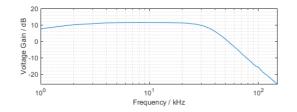

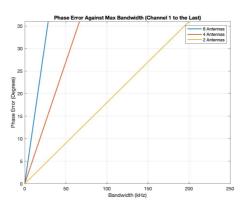

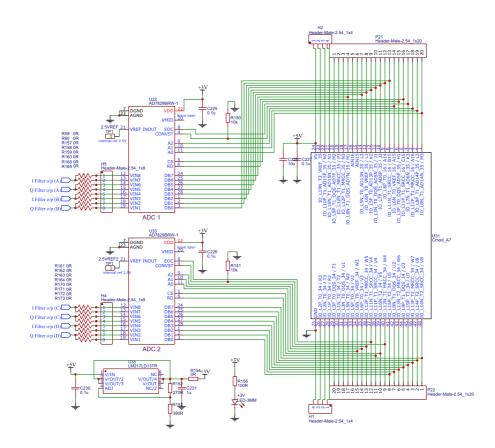

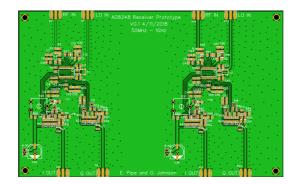

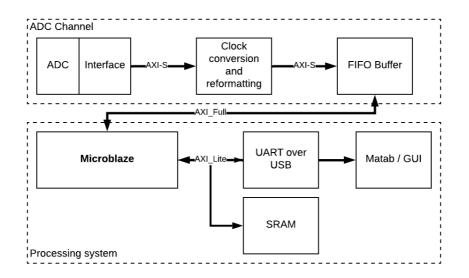

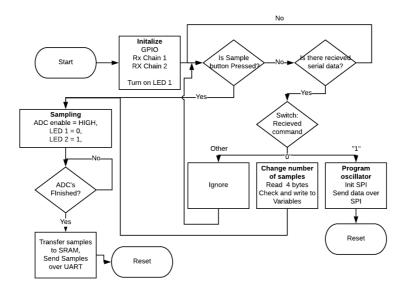

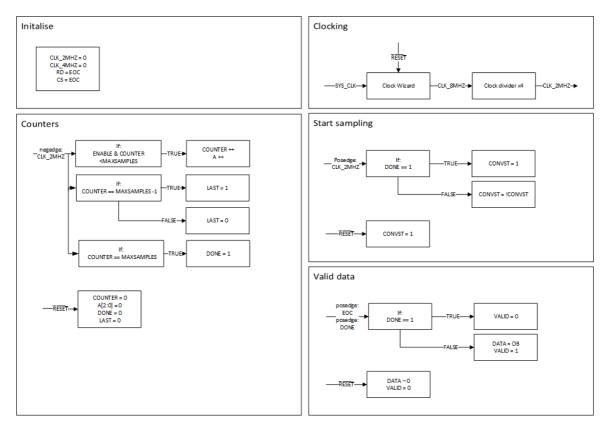

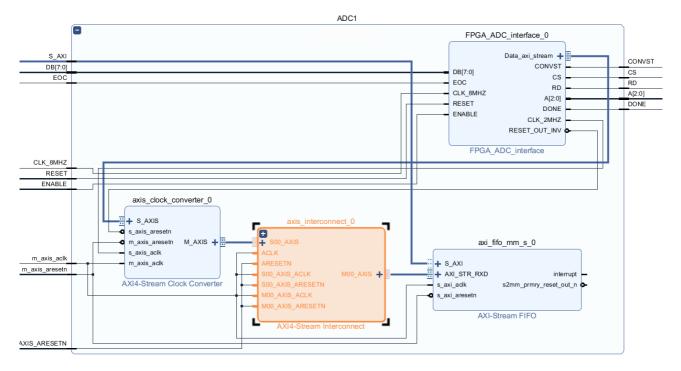

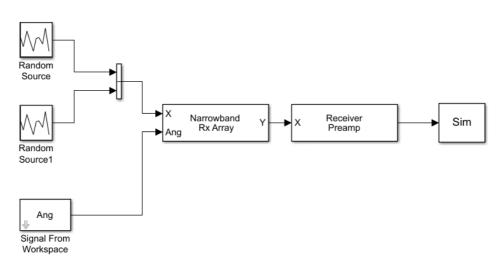

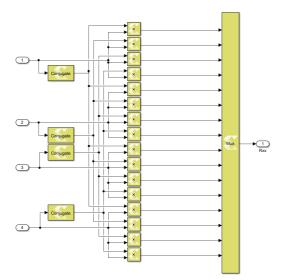

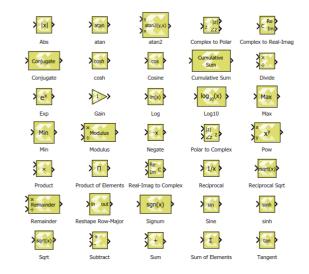

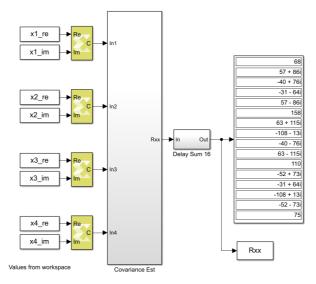

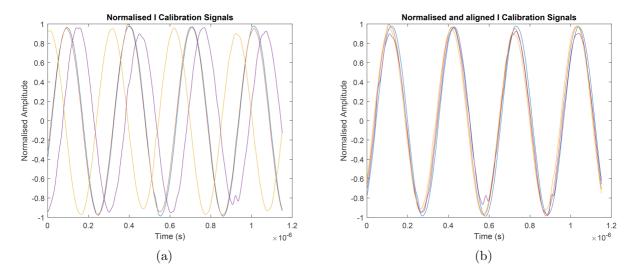

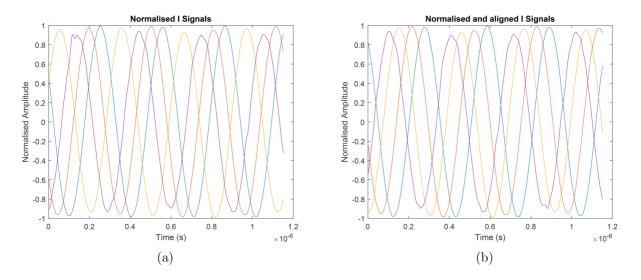

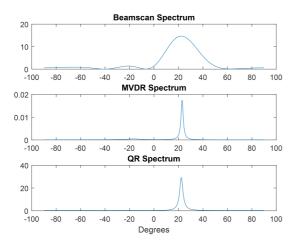

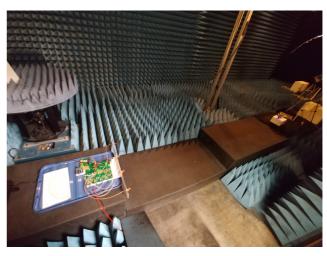

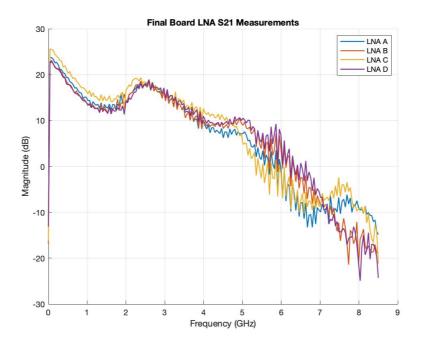

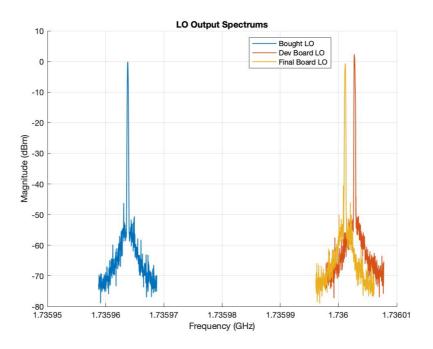

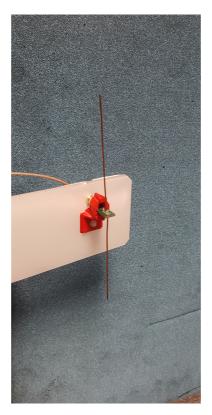

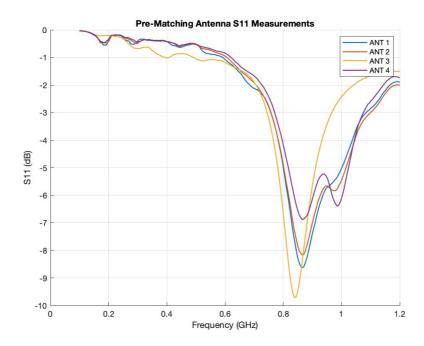

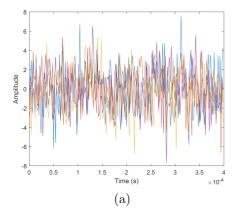

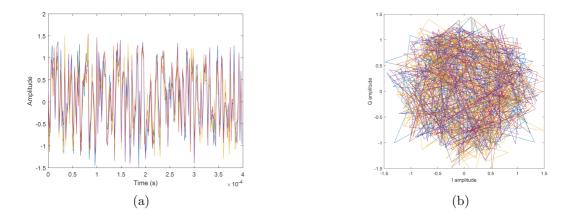

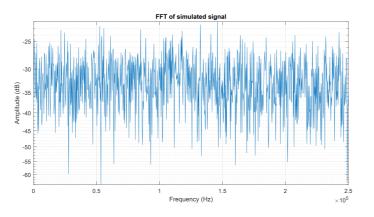

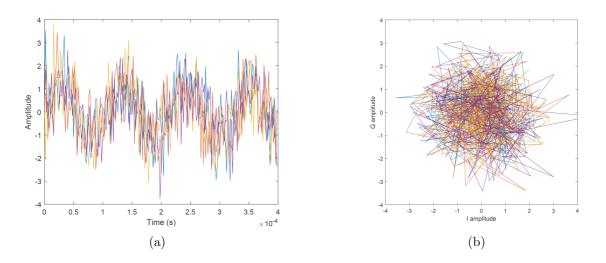

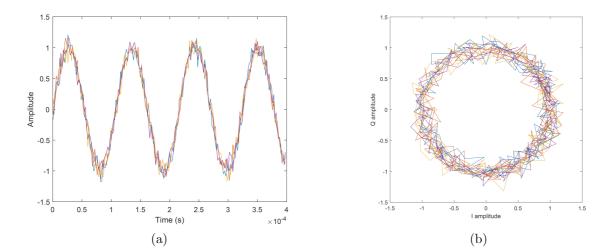

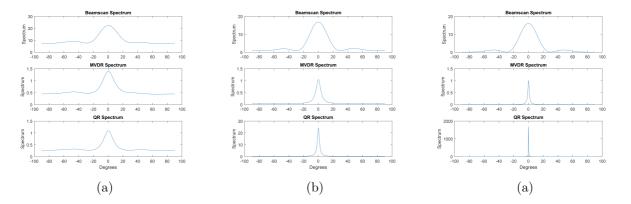

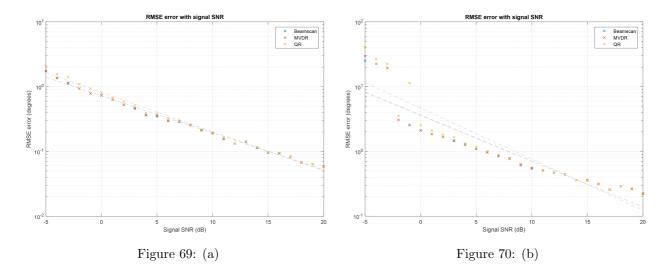

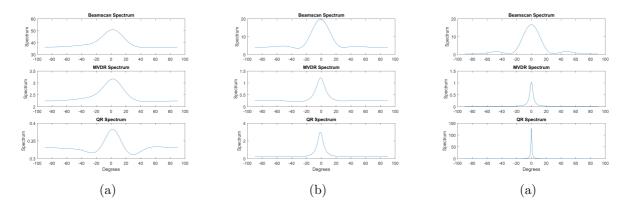

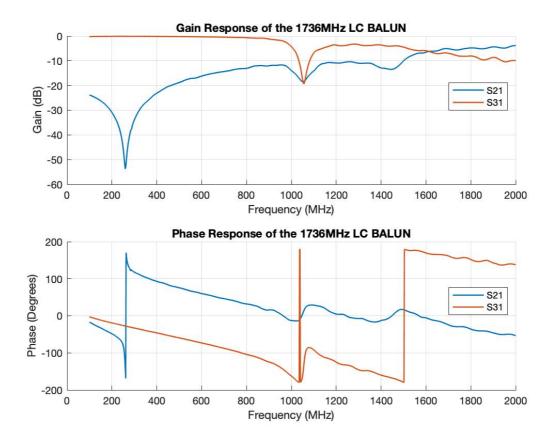

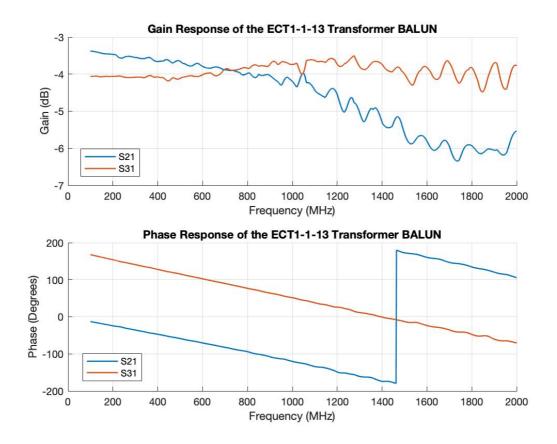

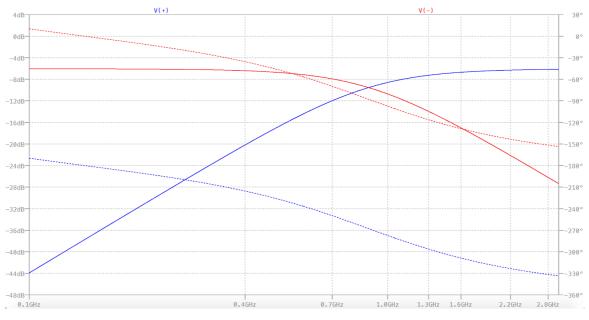

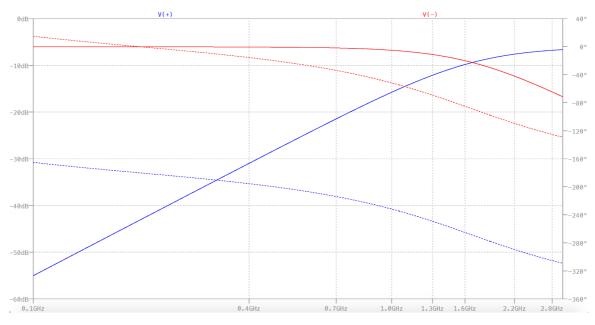

Digital signals processing (DSP) offers many advantages over analogue processing. DSP can offer great accuracy, repeatability and flexibility as operations are performed mathematically compared to analogue processing which relies on the tolerance of circuit components to achieve these characteristics [13]. For DSP design two processors are focused on the single-core microprocessor architecture and the field programmable gate array (FPGA). The microprocessor performs a series of sequential operations chosen from a set of instructions determined during the design of the device. The FPGA however, uses an array of logic blocks that are connected at the time of programming allowing for greater flexibility and the use of real-time sequential operations.